Khi học bất kì con vi điều khiển nào đầu tiên chúng ta cần tìm hiểu cấu trúc và bản đồ bộ nhớ (memory maps) của vi điều khiển đó. Điều này sẽ giúp chúng ta nắm rõ được cách thức nó hoạt động, chạy chương trình, chạy code như thế nào.

Bài viết nằm trong Serie Học STM32 từ A tới Z

Kiến trúc vi điều khiển STM32F103

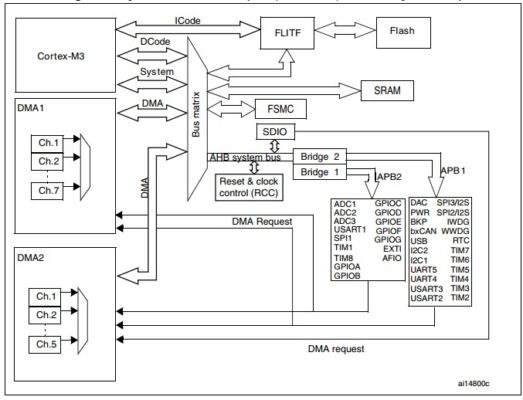

Sơ đồ tổng quan

• 4 masters:

– Cortex®-M3 core DCode bus (D-bus) và System bus (S-bus)

– GP-DMA1 & 2 (general-purpose DMA)

• 4 slaves:

– Internal SRAM: Ram nội

– Internal Flash memory: Bộ nhớ Flash nội

– FSMC: Giao thức kết nối bộ nhớ ngoài

– AHB to APBx (APB1 or APB2), kết nối tới các ngoại vi APB

Dcode Bus

Kết nối lõi Cortex M3 với bộ nhớ Flash và các chuẩn kết nối dữ liệu bộ nhớ.

System Bus

Bus này kết nối bus hệ thống của lõi Cortex®-M3 (bus thiết bị ngoại vi) với BusMatrix quản lý data giữ Core và DMA

DMA bus

Bus này kết nối giao diện chủ AHB của DMA với BusMatrix quản lý quyền truy cập của CPU DCode và DMA tới SRAM, bộ nhớ Flash và thiết bị ngoại vi.

BusMatrix

BusMatrix quản lý việc phân xử truy cập giữa bus hệ thống lõi và bus chủ DMA. Nó sử dụng thuật toán Round Robin. Trong các thiết bị kết nối, BusMatrix bao gồm năm bus master (CPU DCode, bus hệ thống, Ethernet DMA, DMA1 và bus DMA2) và ba slave (FLITF, SRAM và AHB2APB).

Trong các thiết bị khác, BusMatrix bao gồm master (CPU DCode, bus hệ thống, bus DMA1 và bus DMA2) và bốn slave (\FLITF, SRAM, FSMC và AHB2APB). Các thiết bị ngoại vi AHB được kết nối trên bus hệ thống thông qua BusMatrix để cho phép truy cập DMA.

AHB/APB bridges (APB)

Hai cầu AHB / APB cung cấp kết nối đồng bộ đầy đủ giữa AHB và 2 bus APB. APB1 được giới hạn ở 36 MHz, APB2 hoạt động ở tốc độ tối đa (lên đến 72 MHz tùy thuộc vào thiết bị).

Sau mỗi lần reset thiết bị, tất cả các đồng hồ ngoại vi đều bị tắt (ngoại trừ SRAM và FLITF). Trước khi sử dụng thiết bị ngoại vi, bạn phải bật clock của nó trong thanh ghi RCC_AHBENR, RCC_APB2ENR hoặc RCC_APB1ENR

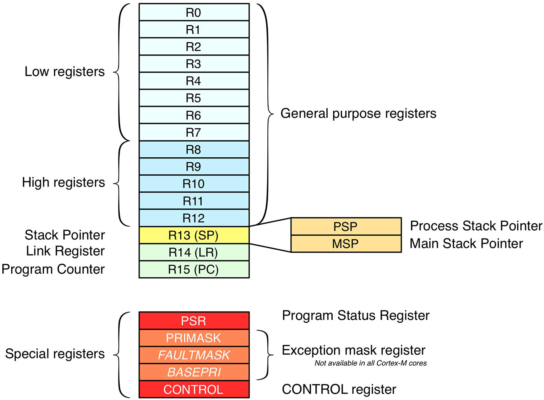

Core registers ( Thanh ghi lõi)

R0-R12 là các thanh ghi có mục đích chung và có thể được sử dụng làm toán hạng cho các lệnh ARM.

Một số thanh ghi có mục đích chung, có thể được trình biên dịch sử dụng như các thanh ghi có chức năng đặc biệt.

Thanh ghi R13 là thanh ghi Stack Pointer (SP), có cấu trúc dạng ngăn xếp, nghĩa là vào đầu tiên thì ra sau cùng Fist in Last Out

Bản đồ bộ nhớ STM32f103 (Memory Maps)

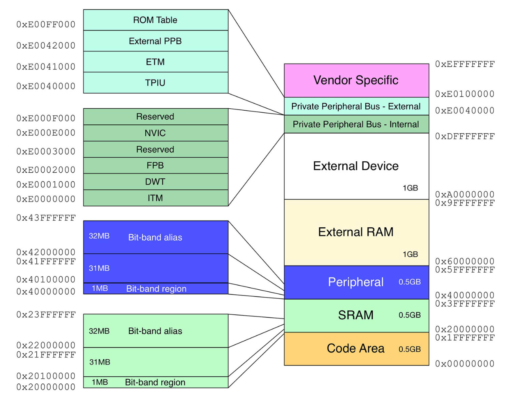

ARM xác định một không gian địa chỉ bộ nhớ được tiêu chuẩn hóa chung cho tất cả các lõi Cortex-M, điều này thực thi khả năng di động của code giữa các nhà sản xuất khác nhau.

Không gian bộ nhớ (memory) được thiết kế chia thành một số vùng khác nhau. Code, SRAM, Peripherals, External RAM, External Device, Pravite peripheral bus internal and external, Vendor Specific như hình sau:

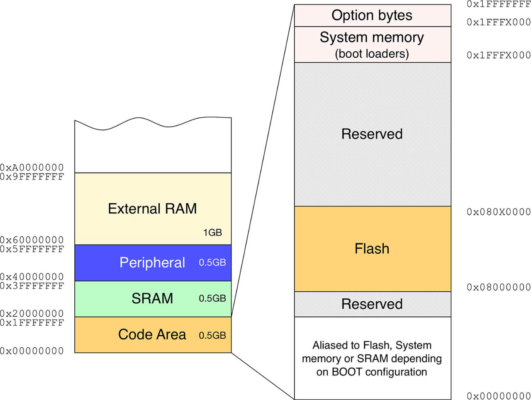

Code Area

512MB đầu tiên được dành riêng cho vùng code.Tất cả các bộ xử lý Cortex-M ánh xạ vùng mã bắt đầu từ địa chỉ 0x0000 0000.Khu vực này cũng bao gồm con trỏ đến đầu ngăn xếp (thường được đặt trong SRAM) và bảng vectơ.

Trên thực tế, đối với tất cả các thiết bị STM32, một vùng bắt đầu từ địa chỉ 0x0800 0000 được liên kết với bộ nhớ FLASH MCU bên trong và nó là vùng chứa mã chương trình. Nhờ cấu hình khởi động cụ thể, khu vực này cũng được đặt bí danh từ địa chỉ 0x0000 0000.

Điều này có nghĩa là hoàn toàn có thể tham chiếu đến nội dung của bộ nhớ FLASH bắt đầu từ địa chỉ 0x0800 0000 và địa chỉ 0x0000 0000

Hai phần cuối dành riêng cho bộ nhớ Hệ thống (System Memmory) và Byte tùy chọn ( Options Byte)

System Memory – Bộ nhớ hệ thống

Bộ nhớ hệ thống là vùng ROM dành riêng cho bộ nạp khởi động (Boot Loader). Mỗi họ STM32 cung cấp một số Boot Loader khác nhau được lập trình sẵn vào chip trong quá trình sản xuất. Những Boot Loader này có thể được sử dụng để tải code từ một số thiết bị ngoại vi, bao gồm USART, USB và CAN Bus.

Option Bytes – Vùng tùy chọn byte

Vùng byte tùy chọn chứa một loạt cờ bit có thể được sử dụng để định cấu hình một số khía cạnh của MCU (như bảo vệ đọc ghi FLASH, v.v.)

SRAM Area

Sram là gì?

SRAM là viết tắt của Static random-access memory (Bộ nhớ truy cập ngẫu nhiên tĩnh hay RAM tĩnh). SRAM lưu giữ các bit dữ liệu trong bộ nhớ miễn là nguồn điện được cung cấp đầy đủ. Không giống như DRAM, lưu bit dữ liệu trong các pin chứa tụ điện và bóng bán dẫn, SRAM không cần phải làm tươi theo định kỳ.

Sram trong STM32 tổ chức ra sao?

SRAM bắt đầu từ địa chỉ 0x2000 0000 và có thể kéo dài đến 0x3FFF FFFF. SRAM được sử dụng để truy xuất data và bộ nhớ stack.

Tuy nhiên, địa chỉ kết thúc thực tế phụ thuộc vào số lượng SRAM nội bộ khả dụng. Ví dụ: giả sử MCU STM32F103RB với 20KB SRAM, chúng ta có địa chỉ cuối cùng là 0x200013FF. Cố gắng truy cập vào một vị trí bên ngoài khu vực này sẽ gây ra lỗi Bus Fault.

Trong vùng nhớ này, 1MB đầu tiên được chia thành vùng Bit-band. Mỗi bit trong vùng Bit-band được đánh địa chỉ độc lập. Bạn cũng có thể thực thi code từ vùng nhớ SRAM, Vi xử lý không giới hạn việc thực thi chương trình từ đây.

Peripheral Area

Mọi thiết bị ngoại vi được cung cấp bởi MCU (bộ định thời, I2C và SPI, USART, v.v.) đều được đặt bí danh cho vùng này. Chi tiết về các thanh ghi của ngoại vi sẽ phụ thuộc vào từng dòng vi điều khiển khác nhau. Các bạn nên đọc tài liệu của từng loại để hiểu rõ hơn

External RAM Area

Nếu như bộ nhớ RAM được tích hợp sẵn trên vi điều khiển không đủ và bạn muốn kết nối với 1 bộ nhớ RAM ngoài thì bạn có thể khai thác được chức năng của vùng nhớ này.

Các thiết bị Cortex-M có thể thực thi mã và tải / lưu trữ dữ liệu từ các bộ nhớ ngoài, giúp mở rộng tài nguyên bộ nhớ trong, thông qua giao diện EMI / FSMC.

Kết

Nắm rõ cấu trúc và bộ nhớ (memory) của stm32 sẽ giúp ích rất nhiều trong việc hiểu sâu về vi điều khiển, từ đó trở thành một lập trình viên ưu tú hơn. Nên nhớ để nâng cao trình độ của mình, chúng ta cần phải đào sâu nghiện cứu những thứ tưởng chừng rất đơn

Nếu bài viết này có ích hãy chia sẻ nó và tham gia hội anh em Nghiện Lập Trình để giao lưu nhé!